SBAS184C - MARCH 2001 - REVISED SEPTEMBER 2007

# 24-Bit, 20kHz, Low-Power ANALOG-TO-DIGITAL CONVERTER

## **FEATURES**

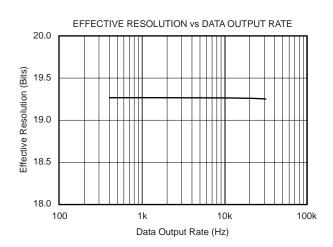

- 24 BITS—NO MISSING CODES

- 19 BITS EFFECTIVE RESOLUTION UP TO 20kHz DATA RATE

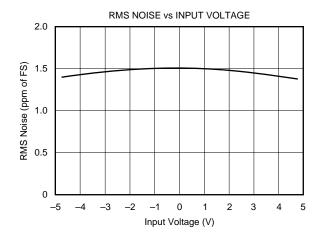

- LOW NOISE: 1.5ppm

- DIFFERENTIAL INPUTS

- INL: 15ppm (max)

- EXTERNAL REFERENCE (0.5V to 5V)

- POWER-DOWN MODE

- SYNC MODE

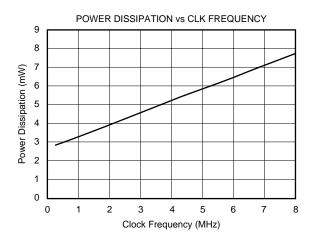

- LOW POWER: 8mW at 20kHz

- 5mW at 10kHz

## **APPLICATIONS**

- CARDIAC DIAGNOSTICS

- DIRECT THERMOCOUPLE INTERFACES

- BLOOD ANALYSIS

- INFRARED PYROMETERS

- LIQUID/GAS CHROMATOGRAPHY

- PRECISION PROCESS CONTROL

### DESCRIPTION

The ADS1251 is a precision, wide dynamic range, delta-sigma, Analog-to-Digital (A/D) converter with 24-bit resolution operating from a single +5V supply. The delta-sigma architecture features wide dynamic range, and 24 bits of no missing code performance. Effective resolution of 19 bits (1.5ppm of rms noise) is achieved at conversion rates up to 20kHz.

The ADS1251 is designed for high-resolution measurement applications in cardiac diagnostics, smart transmitters, industrial process control, weigh scales, chromatography, and portable instrumentation. The converter includes a flexible, 2-wire synchronous serial interface for low-cost isolation.

The ADS1251 is a single-channel converter and is offered in an SO-8 package. It is pin-compatible with the faster ADS1252 (41.7kHz data rate).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

#### **ABSOLUTE MAXIMUM RATINGS(1)**

| ±10mA, Continuous                                             | 3 |

|---------------------------------------------------------------|---|

| Voltage GND - 0.3V to V <sub>DD</sub> + 0.3V                  | / |

| V <sub>DD</sub> to GND0.3V to 6V                              | / |

| V <sub>REF</sub> Voltage to GND0.3V to V <sub>DD</sub> + 0.3V | / |

| Digital Input Voltage to GND0.3V to V <sub>DD</sub> + 0.3V    | / |

| Digital Output Voltage to GND0.3V to V <sub>DD</sub> + 0.3V   | / |

| Operating Temperature40°C to 85°C                             | ) |

| Lead Temperature (soldering, 10s) +300°C                      | ) |

| Power Dissipation 500mW                                       | / |

NOTE: (1) Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

# ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### PACKAGE/ORDERING INFORMATION(1)

| PRODUCT | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER       | TRANSPORT<br>MEDIA, QUANTITY      |

|---------|--------------|-----------------------|-----------------------------------|--------------------|--------------------------|-----------------------------------|

| ADS1251 | SO-8<br>"    | D<br>"                | -40°C to +85°C                    | ADS1251U<br>"      | ADS1251U<br>ADS1251U/2K5 | Rails, 100<br>Tape and Reel, 2500 |

NOTE: (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

#### **PRODUCT FAMILY**

| PRODUCT | # OF INPUTS    | MAXIMUM DATA RATE | COMMENTS                                      |

|---------|----------------|-------------------|-----------------------------------------------|

| ADS1250 | 1 Differential | 25.0kHz           | Includes PGA from 1 to 8                      |

| ADS1251 | 1 Differential | 26.8kHz           |                                               |

| ADS1252 | 1 Differential | 41.7kHz           |                                               |

| ADS1253 | 4 Differential | 20.8kHz           |                                               |

| ADS1254 | 4 Differential | 20.8kHz           | Includes Separate Analog and Digital Supplies |

## **ELECTRICAL CHARACTERISTICS**

All specifications at  $T_{MIN}$  to  $T_{MAX}$ ,  $V_{DD}$  = +5V, CLK = 8MHz, and  $V_{REF}$  = 4.096, unless otherwise specified.

|                                      |                                             |      | ADS1251U          |                 |                 |

|--------------------------------------|---------------------------------------------|------|-------------------|-----------------|-----------------|

| PARAMETER                            | CONDITIONS                                  | MIN  | TYP               | MAX             | UNITS           |

| ANALOG INPUT                         |                                             |      |                   |                 |                 |

| Full-Scale Input Voltage             | $+V_{IN} - (-V_{IN})$                       |      | ±V <sub>REF</sub> |                 | V               |

| Absolute Input Voltage               | +V <sub>IN</sub> or -V <sub>IN</sub> to GND | -0.3 |                   | V <sub>DD</sub> | V               |

| Differential Input Impedance         | CLK = 3.84kHz                               |      | 430               |                 | MΩ              |

|                                      | CLK = 1MHz                                  |      | 1.7               |                 | MΩ              |

|                                      | CLK = 8MHz                                  |      | 210               |                 | kΩ              |

| Input Capacitance                    |                                             |      | 6                 |                 | pF              |

| Input Leakage                        | At +25°C                                    |      | 5                 | 50              | pА              |

|                                      | At T <sub>MIN</sub> to T <sub>MAX</sub>     |      |                   | 1               | nA              |

| DYNAMIC CHARACTERISTICS              |                                             |      |                   |                 |                 |

| Data Rate                            |                                             |      |                   | 20.8            | kHz             |

| Bandwidth                            | -3dB, CLK = 8MHz                            | 4.24 |                   |                 | kHz             |

| Serial Clock (SCLK)                  |                                             |      |                   | 8               | MHz             |

| System Clock Input (CLK)             |                                             |      |                   | 8               | MHz             |

| ACCURACY                             |                                             |      |                   |                 |                 |

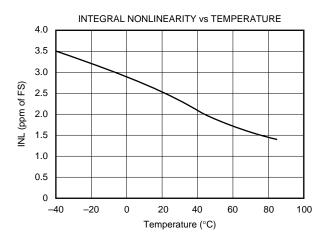

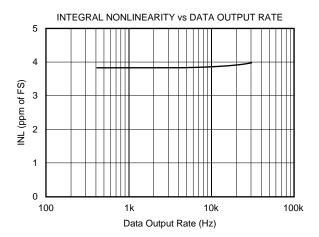

| Integral Nonlinearity                | Differential Input                          |      | ±0.0002           | ±0.0015         | % of FSR        |

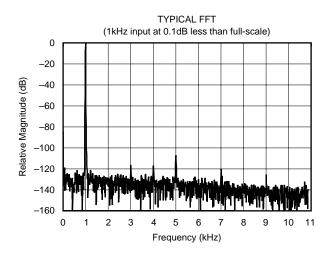

| THD                                  | 1kHz Input; 0.1dB below FS                  |      | 105               |                 | dB              |

| Noise                                |                                             |      | 1.5               | 2.5             | ppm of FSR, rms |

| Resolution                           |                                             | 24   |                   |                 | Bits            |

| No Missing Codes                     |                                             | 24   |                   |                 | Bits            |

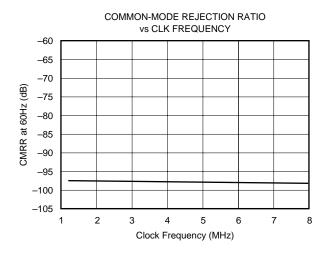

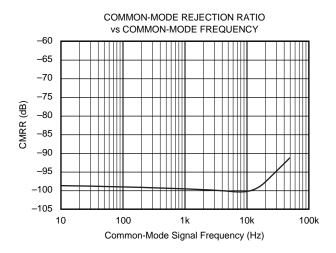

| Common-Mode Rejection                | 60Hz, AC                                    | 90   | 98                |                 | dB              |

| Gain Error                           |                                             |      | 0.1               | 1               | % of FSR        |

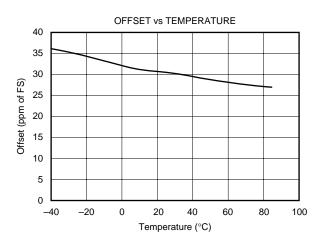

| Offset Error                         |                                             |      | ±30               | ±100            | ppm of FSR      |

| Gain Sensitivity to V <sub>REF</sub> |                                             |      | 1:1               |                 |                 |

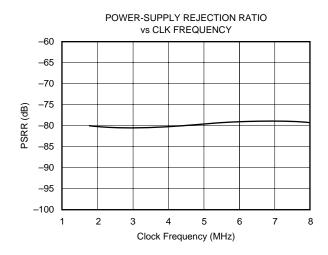

| Power-Supply Rejection Ratio         |                                             | 70   | 80                |                 | dB              |

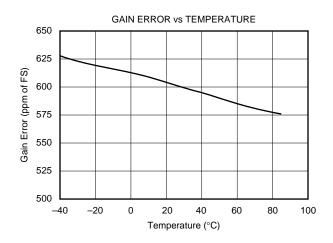

| PERFORMANCE OVER TEMPERATURE         |                                             |      |                   |                 |                 |

| Offset Drift                         |                                             |      | 0.07              |                 | ppm/°C          |

| Gain Drift                           |                                             |      | 0.4               |                 | ppm/°C          |

# **ELECTRICAL CHARACTERISTICS (Cont.)**

All specifications at  $T_{MIN}$  to  $T_{MAX}$ ,  $V_{DD}$  = +5V, CLK = 8MHz, and  $V_{REF}$  = 4.096, unless otherwise specified.

|                              |                       |       | ADS1251U             |                 |       |

|------------------------------|-----------------------|-------|----------------------|-----------------|-------|

| PARAMETER                    | CONDITIONS            | MIN   | TYP                  | MAX             | UNITS |

| VOLTAGE REFERENCE            |                       |       |                      |                 |       |

| $V_{REF}$                    |                       | 0.5   | 4.096                | V <sub>DD</sub> | V     |

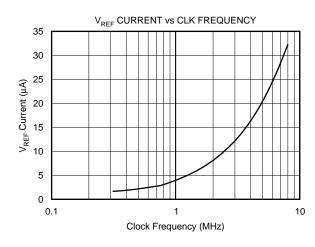

| Load Current                 |                       |       | 32                   |                 | μΑ    |

| DIGITAL INPUT/OUTPUT         |                       |       |                      |                 |       |

| Logic Family                 |                       |       | CMOS                 |                 |       |

| Logic Level: V <sub>IH</sub> |                       | +4.0  |                      | $+V_{DD} + 0.3$ | V     |

| $V_{IL}$                     |                       | -0.3  |                      | +0.8            | V     |

| $V_{OH}$                     | $I_{OH} = -500 \mu A$ | +4.5  |                      |                 | V     |

| $V_{OL}$                     | $I_{OL} = 500 \mu A$  |       |                      | 0.4             | V     |

| Input (SCLK, CLK) Hysteresis |                       |       | 0.6                  |                 | V     |

| Data Format                  |                       | Offse | et Binary Two's Comp | lement          |       |

| POWER-SUPPLY REQUIREMENTS    |                       |       |                      |                 |       |

| Operation                    |                       | +4.75 | +5                   | +5.25           | VDC   |

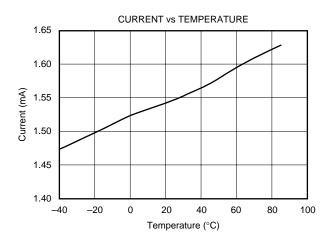

| Quiescent Current            | $V_{DD} = +5VDC$      |       | 1.5                  | 2               | mA    |

| Operating Power              |                       |       | 7.5                  | 10              | mW    |

| Power-Down Current           |                       |       | 0.4                  | 1               | μΑ    |

| TEMPERATURE RANGE            |                       |       |                      |                 |       |

| Operating                    |                       | -40   |                      | +85             | °C    |

| Storage                      |                       | -60   |                      | +100            | °C    |

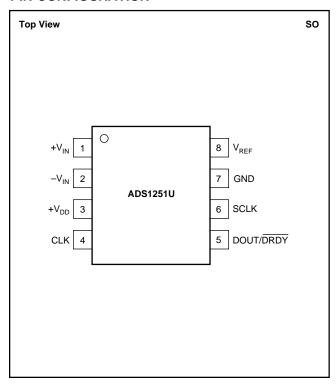

#### **PIN CONFIGURATION**

#### **PIN DESCRIPTIONS**

| PIN | NAME             | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | +V <sub>IN</sub> | Analog Input: Positive Input of the Differential Analog Input                                                                                                                                                                                                                                                                                                                                                            |

| 2   | -V <sub>IN</sub> | Analog Input: Negative Input of the Differential Analog Input.                                                                                                                                                                                                                                                                                                                                                           |

| 3   | +V <sub>DD</sub> | Input: Power-Supply Voltage, +5V                                                                                                                                                                                                                                                                                                                                                                                         |

| 4   | CLK              | Digital Input: Device System Clock. The system clock is in the form of a CMOS-compatible clock. This is a Schmitt-Trigger input.                                                                                                                                                                                                                                                                                         |

| 5   | DOUT/DRDY        | Digital Output: Serial Data Output/Data Ready. This output indicates that a new output word is available from the ADS1251 data output register. The serial data is clocked out of the serial data output shift register using SCLK.                                                                                                                                                                                      |

| 6   | SCLK             | Digital Input: Serial Clock. The serial clock is in the form of a CMOS-compatible clock. The serial clock operates independently from the system clock, therefore, it is possible to run SCLK at a higher frequency than CLK. The normal state of SCLK is LOW. Holding SCLK HIGH will either initiate a modulator reset for synchronizing multiple converters or enter power-down mode. This is a Schmitt-Trigger input. |

| 7   | GND              | Input: Ground                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8   | $V_{REF}$        | Analog Input: Reference Voltage Input                                                                                                                                                                                                                                                                                                                                                                                    |

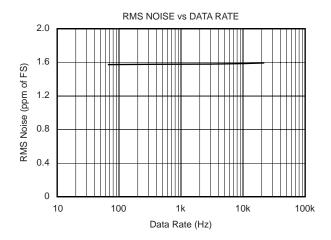

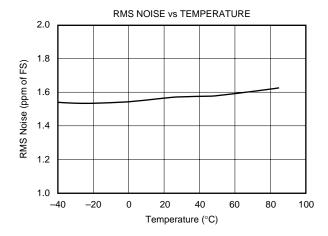

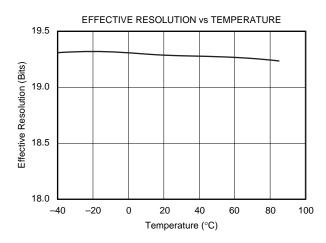

## TYPICAL CHARACTERISTICS

At  $T_A$  = +25°C,  $V_{DD}$  = +5V, CLK = 8MHz, and  $V_{REF}$  = 4.096, unless otherwise specified.

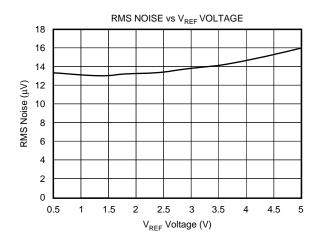

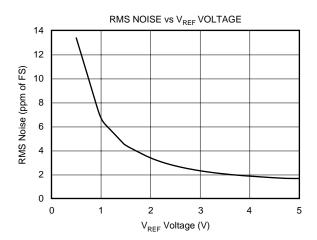

# **TYPICAL CHARACTERISTICS (Cont.)**

At  $T_A$  = +25°C,  $V_{DD}$  = +5V, CLK = 8MHz, and  $V_{REF}$  = 4.096, unless otherwise specified.

# **TYPICAL CHARACTERISTICS (Cont.)**

At  $T_A$  = +25°C,  $V_{DD}$  = +5V, CLK = 8MHz, and  $V_{REF}$  = 4.096, unless otherwise specified.

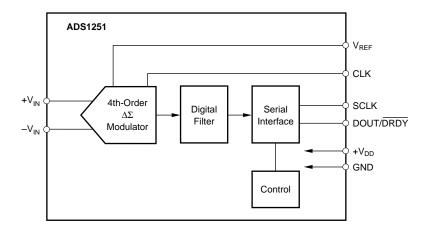

## THEORY OF OPERATION

The ADS1251 is a precision, high-dynamic range, 24-bit, delta-sigma, A/D converter capable of achieving very high-resolution digital results at high data rates. The analog input signal is sampled at a rate determined by the frequency of the system clock (CLK). The sampled analog input is modulated by the delta-sigma A/D modulator, which is followed by a digital filter. A Sinc<sup>5</sup> digital low-pass filter processes the output of the delta-sigma modulator and writes the result into the data-output register. The DOUT/DRDY pin is pulled LOW, indicating that new data is available to be read by the external microcontroller/microprocessor. As shown in the block diagram on the front page, the main functional blocks of the ADS1251 are the 4th-order delta-sigma modulator, a digital filter, control logic, and a serial interface. Each of these functional blocks is described in the following sections.

#### **ANALOG INPUT**

The ADS1251 contains a fully differential analog input. In order to provide low system noise, common-mode rejection of 98dB, and excellent power-supply rejection, the design topology is based on a fully differential switched-capacitor architecture. The bipolar input voltage range is from -4.096 to +4.096V, when the reference input voltage equals +4.096V. The bipolar range is with respect to  $-V_{IN}$ , and not with respect to GND.

The differential input impedance of the analog input changes with the ADS1251 system clock frequency (CLK). The relationship is:

Impedance ( $\Omega$ ) = (8MHz/CLK) • 210,000

See application note *Understanding the ADS1251*, *ADS1253*, and *ADS1254 Input Circuitry* (SBAA086), available for download from TI's web site www.ti.com.

With regard to the analog-input signal, the overall analog performance of the device is affected by three items. First, the input impedance can affect accuracy. If the source impedance of the input signal is significant, or if there is passive filtering prior to the ADS1251, a significant portion of the signal can be lost across this external impedance. The magnitude of the effect is dependent on the desired system performance.

Second, the current into or out of the analog inputs must be limited. Under no conditions should the current into or out of the analog inputs exceed 10mA.

Third, to prevent aliasing of the input signal, the bandwidth of the analog-input signal must be band-limited; the bandwidth is a function of the system clock frequency. With a system clock frequency of 8MHz, the data-output rate is 20.8kHz with a -3dB frequency of 4.24kHz. The -3dB frequency scales with the system clock frequency.

To ensure the best linearity of the ADS1251, and to maximize the elimination of even-harmonic noise errors, a fully differential signal is recommended.

For more information about the ADS1251 input structure, please refer to application note SBAA086 found at www.ti.com.

#### **BIPOLAR INPUT**

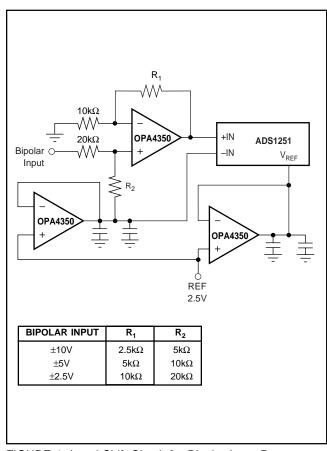

Each of the differential inputs of the ADS1251 must stay between -0.3V and  $V_{DD}.$  With a reference voltage at less than half of  $V_{DD},$  one input can be tied to the reference voltage, and the other input can range from 0V to  $2 \bullet V_{REF}.$  By using a three op amp circuit featuring a single amplifier and four external resistors, the ADS1251 can be configured to accept bipolar inputs referenced to ground. The conventional  $\pm 2.5V,\,\pm 5V,\,$  and  $\pm 10V$  input ranges can be interfaced to the ADS1251 using the resistor values shown in Figure 1.

FIGURE 1. Level-Shift Circuit for Bipolar Input Ranges.

#### **DELTA-SIGMA MODULATOR**

The ADS1251 operates from a nominal system clock frequency of 8MHz. The modulator frequency is fixed in relation to the system clock frequency. The system clock frequency is divided by 6 to derive the modulator frequency ( $f_{\text{MOD}}$ ). Therefore, with a system clock frequency of 8MHz, the modulator frequency is 1.333MHz. Furthermore, the oversampling ratio of the modulator is fixed in relation to the modulator frequency. The oversampling ratio of the modulator is 64, and with the modulator frequency running at 1.333MHz, the data rate is 20.8kHz. Using a slower system clock frequency will result in a lower data output rate, as shown in Table I.

| CLK (MHz)                    | DATA OUTPUT RATE (Hz) |

|------------------------------|-----------------------|

| 8(1)                         | 20,833                |

| 7.372800(1)                  | 19,200                |

| 6.144000 <sup>(1)</sup>      | 16,000                |

| 6.000000(1)                  | 15,625                |

| 4.915200 <sup>(1)</sup>      | 12,800                |

| 3.686400 <sup>(1)</sup>      | 9600                  |

| 3.072000(1)                  | 8000                  |

| 2.457600 <sup>(1)</sup>      | 6400                  |

| 1.843200 <sup>(1)</sup>      | 4800                  |

| 0.921600                     | 2400                  |

| 0.460800                     | 1200                  |

| 0.384000                     | 1000                  |

| 0.192000                     | 500                   |

| 0.038400                     | 100                   |

| 0.023040                     | 60                    |

| 0.019200                     | 50                    |

| 0.011520                     | 30                    |

| 0.009600                     | 25                    |

| 0.007680                     | 20                    |

| 0.006400                     | 16.67                 |

| 0.005760                     | 15                    |

| 0.004800                     | 12.50                 |

| 0.003840                     | 10                    |

| NOTE: (1) Standard Clock Osc | sillator.             |

TABLE I. CLK Rate versus Data Output Rate.

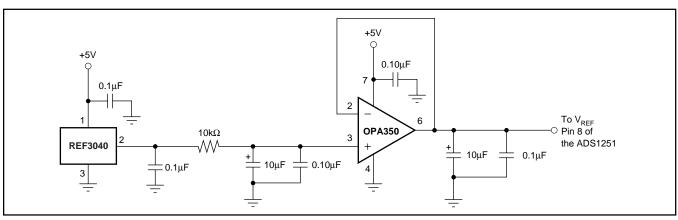

#### REFERENCE INPUT

The reference input takes an average current of  $32\mu A$  with a 8MHz system clock. This current will be proportional to the system clock. A buffered reference is recommended for the ADS1251. The recommended reference circuit is shown in Figure 2.

Reference voltages higher than 4.096V will increase the full-scale range, while the absolute internal circuit noise of the converter remains the same. This will decrease the noise in terms of ppm of full-scale, which increases the effective resolution (see typical characteristic *RMS Noise vs V\_{REF} Voltage*).

#### **DIGITAL FILTER**

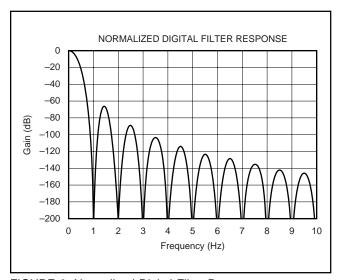

The digital filter of the ADS1251, referred to as a Sinc<sup>5</sup> filter, computes the digital result based on the most recent outputs from the delta-sigma modulator. At the most basic level, the digital filter can be thought of as averaging the modulator results in a weighted form and presenting this average as the digital output. The digital output rate, or data rate, scales directly with the system clock frequency. This allows the data output rate to be changed over a very wide range (five orders of magnitude) by changing the system clock frequency. However, it is important to note that the –3dB point of the filter is 0.2035 times the data output rate, so the data output rate should allow for sufficient margin to prevent attenuation of the signal of interest.

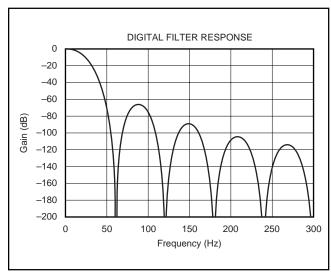

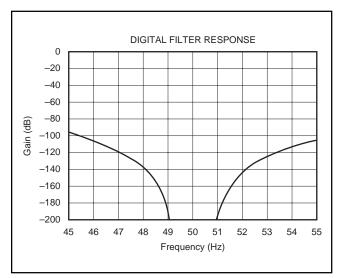

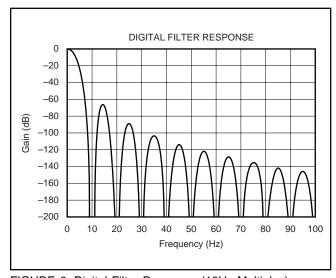

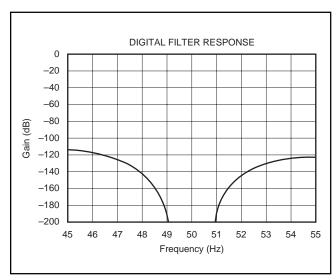

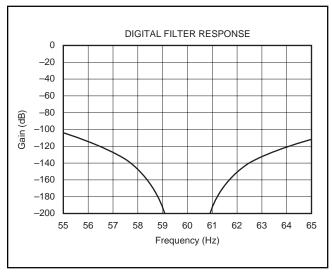

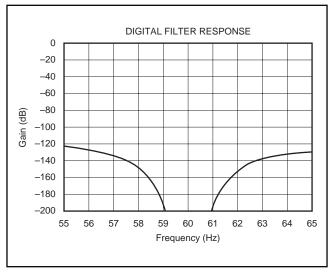

As the conversion result is essentially an average, the data-output rate determines the location of the resulting notches in the digital filter (see Figure 3). Note that the first notch is located at the data output rate frequency, and subsequent notches are located at integer multiples of the data output rate; this allows for rejection of not only the fundamental frequency, but also harmonic frequencies. In this manner, the data output rate can be used to set specific notch frequencies in the digital filter response.

For example, if the rejection of power-line frequencies is desired, then the data output rate can simply be set to the power-line frequency. For 50Hz rejection, the system clock

FIGURE 2. Recommended External Voltage Reference Circuit for Best Low-Noise Operation with the ADS1251.

frequency must be 19.200kHz, and this sets the data output rate to 50Hz (see Table I and Figure 4). For 60Hz rejection, the system CLK frequency must be 23.040kHz, and this sets the data-output rate to 60Hz (see Table I and Figure 5). If both 50Hz and 60Hz rejection is required, then the system CLK must be 3.840kHz; this sets the data output rate to 10Hz and rejects both 50Hz and 60Hz (see Table I and Figure 6).

There is an additional benefit in using a lower data output rate. It provides better rejection of signals in the frequency band of interest. For example, with a 50Hz data output rate, a significant signal at 75Hz may alias back into the passband at 25Hz. This is due to the fact that rejection at 75Hz may only be 66dB in the stopband—frequencies higher than the first notch frequency (see Figure 4). However, setting the data output rate to 10Hz provides 135dB rejection at 75Hz (see Figure 6). A similar benefit is gained at frequencies near the data output rate (see Figures 7, 8, 9, and 10). For example, with a 50Hz data output rate, rejection at 55Hz may only be 105dB (see Figure 7). With a 10Hz data output rate, however, rejection at 55Hz will be 122dB (see Figure 8). If a slower data output rate does not meet the system requirements, then the analog front-end can be designed to provide the needed attenuation to prevent aliasing. Additionally, the data output rate may be increased and additional digital filtering may be done in the processor or controller.

Application note A Spreadsheet to Calculate the Frequency Response of the ADS1250-54 (SBAA103) available for download from Tl's web site www.ti.com provides a simple tool for calculating the ADS1250's frequency response for any CLK frequency.

The digital filter is described by the following transfer function:

$$|H(f)| = \begin{vmatrix} \sin\left(\frac{\pi \cdot f \cdot 64}{f_{MOD}}\right) \\ 64 \cdot \sin\left(\frac{\pi \cdot f}{f_{MOD}}\right) \end{vmatrix}^{5}$$

or

$$H(z) = \left(\frac{1 - z^{-64}}{64 \cdot (1 - z^{-1})}\right)^{5}$$

The digital filter requires five conversions to fully settle. The modulator has an oversampling ratio of 64; therefore, it requires 5 • 64, or 320 modulator results (or clocks) to fully settle. As the modulator clock is derived from the system CLK (modulator clock = CLK  $\div$  6), the number of system clocks required for the digital filter to fully settle is 5 • 64 • 6, or 1920 CLKs. This means that any significant step change at the analog input requires five full conversions to settle. However, if the step change at the analog input occurs asynchronously to the DOUT/ $\overline{DRDY}$  pulse, six conversions are required to ensure full settling.

#### **CONTROL LOGIC**

The control logic is used for communications and control of the ADS1251.

#### Power-Up Sequence

Prior to power-up, all digital and analog input pins must be LOW. At the time of power-up, these signal inputs can be biased to a voltage other than 0V; however, they should never exceed +V<sub>DD</sub>.

Once the ADS1251 powers up, the DOUT/DRDY line will pulse LOW on the first conversion for which the data is valid from the analog input signal.

#### DOUT/DRDY

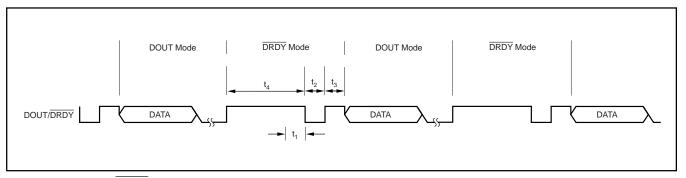

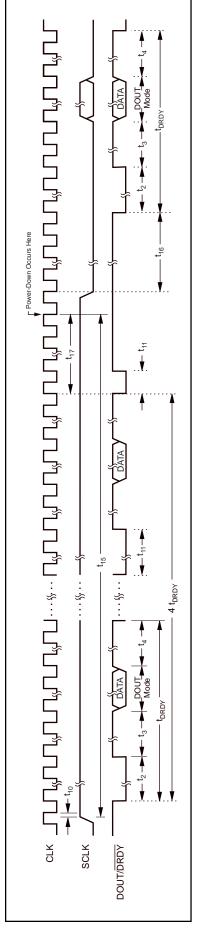

The DOUT/DRDY output signal alternates between two modes of operation. The first mode of operation is the Data Ready mode (DRDY) to indicate that new data has been loaded into the data output register and is ready to be read. The second mode of operation is the Data Output (DOUT) mode and is used to serially shift data out of the Data Output Register (DOR). See Figure 11 for the time domain partitioning of the DRDY and DOUT function.

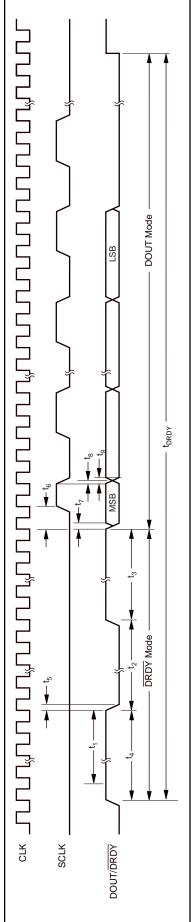

See Figure 12 for the basic timing of  $\overline{DOUT/\overline{DRDY}}$ . During the time defined by  $t_2$ ,  $t_3$ , and  $t_4$ , the  $\overline{DOUT/\overline{DRDY}}$  pin functions in  $\overline{DRDY}$  mode. The state of the  $\overline{DOUT/\overline{DRDY}}$  pin

FIGURE 3. Normalized Digital Filter Response.

FIGURE 5. Digital Filter Response (60Hz).

FIGURE 7. Expanded Digital Filter Response (50Hz with a 50Hz data output rate).

FIGURE 4. Digital Filter Response (50Hz).

FIGURE 6. Digital Filter Response (10Hz Multiples).

FIGURE 8. Expanded Digital Filter Response (50Hz with a 10Hz data output rate).

FIGURE 9. Expanded Digital Filter Response (60Hz with a 60Hz data output rate).

is HIGH prior to the internal transfer of new data to the DOR. The result of the A/D conversion is written to the DOR from the Most Significant Bit (MSB) to the Least Significant Bit (LSB) in the time defined by t<sub>1</sub> (see Figures 11 and 12). The DOUT/DRDY line then pulses LOW for the time defined by t2, and then drives the line HIGH for the time defined by t3 to indicate that new data is available to be read. At this point, the function of the DOUT/DRDY pin changes to DOUT mode. Data is shifted out on the pin after t7. If the MSB is high (because of a negative result) the DOUT/DRDY signal will stay HIGH after the end of time t3. The device communicating with the ADS1251 can provide SCLKs to the ADS1251 after the time defined by t<sub>6</sub>. The normal mode of reading data from the ADS1251 is for the device reading the ADS1251 to latch the data on the rising edge of SCLK (because data is shifted out of the ADS1251 on the falling edge of SCLK). In order to retrieve valid data, the entire DOR must be read before the DOUT/DRDY pin reverts back to DRDY mode.

If SCLKs are not provided to the ADS1251 during the DOUT mode, the MSB of the DOR is present on the DOUT/ $\overline{\text{DRDY}}$  line until the beginning of the time defined by  $t_4$ . If an incomplete read of the ADS1251 takes place while in DOUT mode (that is, less than 24 SCLKs were provided), the state of the last bit read is present on the DOUT/ $\overline{\text{DRDY}}$  line until the beginning of the time defined by  $t_4$ . If more than 24 SCLKs are provided during DOUT mode, the DOUT/ $\overline{\text{DRDY}}$  line stays LOW until the time defined by  $t_4$ .

FIGURE 10. Expanded Digital Filter Response (60Hz with a 10Hz data output rate).

The internal data pointer for shifting data out on  $\overline{DOUT}/\overline{DRDY}$  is reset on the falling edge of the time defined by  $t_1$  and  $t_4$ . This ensures that the first bit of data shifted out of the ADS1251 after  $\overline{DRDY}$  mode is always the MSB of new data.

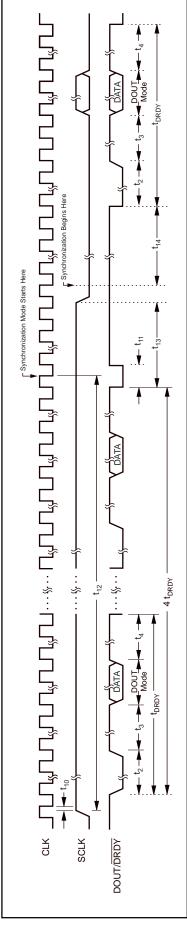

#### SYNCHRONIZING MULTIPLE CONVERTERS

The normal state of SCLK is LOW; however, by holding SCLK HIGH, multiple ADS1251s can be synchronized. This is accomplished by holding SCLK HIGH for at least four, but less than 20, consecutive DOUT/DRDY cycles (see Figure 13). After the ADS1251 circuitry detects that SCLK has been held HIGH for four consecutive DOUT/DRDY cycles, the DOUT/DRDY pin pulses LOW for one CLK cycle and then is held HIGH, and the modulator is held in a reset state. The modulator will be released from reset and synchronization occurs on the falling edge of SCLK. With multiple converters, the falling edge transition of SCLK must occur simultaneously on all devices. It is important to note that prior to synchronization, the DOUT/DRDY pulse of multiple ADS1251s in the system could have a difference in timing up to one DRDY period. Therefore, to ensure synchronization, the SCLK must be held HIGH for at least five DRDY cycles. The first DOUT/DRDY pulse after the falling edge of SCLK occurs at t<sub>14</sub>. The first DOUT/DRDY pulse indicates valid

#### **POWER-DOWN MODE**

The normal state of SCLK is LOW; however, by holding SCLK HIGH, the ADS1251 will enter power-down mode. This is accomplished by holding SCLK HIGH for at least 20 consecutive DOUT/DRDY periods (see Figure 14). After the ADS1251 circuitry detects that SCLK has been held HIGH for four consecutive DOUT/DRDY cycles, the DOUT/DRDY pin pulses LOW for one CLK cycle and then is held HIGH, and the modulator is held in a reset state. If SCLK is held HIGH for an additional 16 DOUT/DRDY periods, the ADS1251 enters power-down mode. The part will be released from power-down mode on the falling edge of SCLK. It is important to note that the DOUT/DRDY pin is held HIGH after four DOUT/DRDY cycles, but power-down mode is not entered for an additional 16 DOUT/DRDY periods. The first DOUT/DRDY pulse after the falling edge of SCLK occurs at t<sub>16</sub> and indicates valid data. Subsequent DOUT/DRDY pulses will occur normally.

#### **SERIAL INTERFACE**

The ADS1251 includes a simple serial interface which can be connected to microcontrollers and digital signal processors in a variety of ways. Communications with the ADS1251 can commence on the first detection of the DOUT/DRDY pulse after power up.

It is important to note that the data from the ADS1251 is a 24-bit result transmitted MSB-first in Offset Binary Two's Complement format, as shown in Table III.

The data must be clocked out before the ADS1251 enters  $\overline{DRDY}$  mode to ensure reception of valid data, as described in the DOUT/ $\overline{DRDY}$  section of this data sheet.

| DIFFERENTIAL VOLTAGE INPUT | DIGITAL OUTPUT (HEX) |

|----------------------------|----------------------|

| +Full-Scale                | 7FFFF <sub>H</sub>   |

| Zero                       | 000000 <sub>H</sub>  |

| -Full-Scale                | 800000 <sub>H</sub>  |

TABLE III. ADS1251 Data Format (Offset Binary Two's Complement).

| SYMBOL            | DESCRIPTION                                                        | MIN        | TYP          | MAX          | UNITS |

|-------------------|--------------------------------------------------------------------|------------|--------------|--------------|-------|

| t <sub>DRDY</sub> | Conversion Cycle                                                   |            | 384 • CLK    |              | ns    |

| DRDY Mode         | DRDY Mode                                                          |            | 36 • CLK     |              | ns    |

| DOUT Mode         | DOUT Mode                                                          |            | 348 • CLK    |              | ns    |

| t <sub>1</sub>    | DOR Write Time                                                     |            | 6 • CLK      |              | ns    |

| t <sub>2</sub>    | DOUT/DRDY LOW Time                                                 |            | 6 • CLK      |              | ns    |

| t <sub>3</sub>    | DOUT/DRDY HIGH Time (Prior to Data Out)                            |            | 6 • CLK      |              | ns    |

| $t_4$             | DOUT/DRDY HIGH Time (Prior to Data Ready)                          |            | 24 • CLK     |              | ns    |

| t <sub>5</sub>    | Rising Edge of CLK to Falling Edge of DOUT/DRDY                    |            |              | 30           | ns    |

| t <sub>6</sub>    | End of DRDY Mode to Rising Edge of First SCLK                      | 30         |              |              | ns    |

| t <sub>7</sub>    | End of DRDY Mode to Data Valid (Propagation Delay)                 |            |              | 30           | ns    |

| t <sub>8</sub>    | Falling Edge of SCLK to Data Valid (Hold Time)                     | 5          |              |              | ns    |

| t <sub>9</sub>    | Falling Edge of SCLK to Next Data Out Valid (Propagation Delay)    |            |              | 30           | ns    |

| t <sub>10</sub>   | SCLK Setup Time for Synchronization or Power Down                  | 30         |              |              | ns    |

| t <sub>11</sub>   | DOUT/DRDY Pulse for Synchronization or Power Down                  |            | 3 • CLK      |              | ns    |

| t <sub>12</sub>   | Rising Edge of SCLK Until Start of Synchronization                 | 1537 • CLK |              | 7679 • CLK   | ns    |

| t <sub>13</sub>   | Synchronization Time                                               | 0.5 • CLK  |              | 6143.5 • CLK | ns    |

| t <sub>14</sub>   | Falling Edge of CLK (After SCLK Goes LOW) Until Start of DRDY Mode |            | 2042.5 • CLK |              | ns    |

| t <sub>15</sub>   | Rising Edge of SCLK Until Start of Power Down                      | 7681 • CLK |              |              | ns    |

| t <sub>16</sub>   | Falling Edge of CLK (After SCLK Goes LOW) Until Start of DRDY Mode |            | 2318.5 • CLK |              | ns    |

| t <sub>17</sub>   | Falling Edge of Last DOUT/DRDY to Start of Power Down              |            | 6144.5 • CLK |              | ns    |

TABLE II. Digital Timing.

FIGURE 11. DOUT/DRDY Partitioning.

FIGURE 12. DOUT/DRDY Timing.

FIGURE 13. Synchronization Mode.

FIGURE 14. Power-Down Mode.

#### **ISOLATION**

The serial interface of the ADS1251 provides for simple isolation methods. The CLK signal can be local to the ADS1251, which then only requires two signals (SCLK and DOUT/DRDY) to be used for isolated data acquisition.

## LAYOUT

#### **POWER SUPPLY**

The power supply must be well-regulated and low-noise. For designs requiring very high resolution from the ADS1251, power-supply rejection will be a concern. Avoid running digital lines under the device as they may couple noise onto the die. High-frequency noise can capacitively couple into the analog portion of the device and will alias back into the passband of the digital filter, affecting the conversion result. This clock noise will cause an offset error.

#### **GROUNDING**

The analog and digital sections of the system design should be carefully and cleanly partitioned. Each section should have its own ground plane with no overlap between them. GND should be connected to the analog ground plane, as well as all other analog grounds. Do not join the analog and digital ground planes on the board, but instead connect the two with a moderate signal trace. For multiple converters, connect the two ground planes at one location as central to all of the converters as possible. In some cases, experimentation may be required to find the best point to connect the two planes together. The printed circuit board can be designed to provide different analog/digital ground connections via short jumpers. The initial prototype can be used to establish which connection works best.

#### **DECOUPLING**

Good decoupling practices should be used for the ADS1251 and for all components in the design. All decoupling capacitors, and specifically the  $0.1\mu F$  ceramic capacitors, should be placed as close as possible to the pin being decoupled. A  $1\mu F$  to  $10\mu F$  capacitor, in parallel with a  $0.1\mu F$  ceramic capacitor, should be used to decouple  $V_{DD}$  to GND.

## SYSTEM CONSIDERATIONS

The recommendations for power supplies and grounding will change depending on the requirements and specific design of the overall system. Achieving 24 bits of noise performance is a great deal more difficult than achieving 12 bits of noise performance. In general, a system can be broken up into four different stages:

- Analog Processing

- · Analog Portion of the ADS1251

- Digital Portion of the ADS1251

- Digital Processing

For the simplest system consisting of minimal analog signal processing (basic filtering and gain), a microcontroller, and one clock source, one can achieve high resolution by powering all components from a common power supply. In addition, all components could share a common ground plane. Thus, there would be no distinctions between analog power and ground, and digital power and ground. The layout should still include a power plane, a ground plane, and careful decoupling. In a more extreme case, the design could include:

- Multiple ADS1251s

- · Extensive Analog Signal Processing

- One or More Microcontrollers, Digital Signal Processors, or Microprocessors

- · Many Different Clock Sources

- · Interconnections to Various Other Systems

High resolution will be very difficult to achieve for this design. The approach would be to break the system into as many different parts as possible. For example, each ADS1251 may have its own analog processing front end.

#### **DEFINITION OF TERMS**

An attempt has been made to use consistent terminology in this data sheet. In that regard, the definition of each term is provided here:

Analog-Input Differential Voltage—for an analog signal that is fully differential, the voltage range can be compared to that of an instrumentation amplifier. For example, if both analog inputs of the ADS1251 are at 2.048V, the differential voltage is 0V. If one analog input is at 0V and the other

analog input is at 4.096V, then the differential voltage magnitude is 4.096V. This is the case regardless of which input is at 0V and which is at 4.096V. The digital-output result, however, is quite different. The analog-input differential voltage is given by the following equation:

$$+V_{IN} - (-V_{IN})$$

A positive digital output is produced whenever the analoginput differential voltage is positive, whereas a negative digital output is produced whenever the differential is negative. For example, a positive full-scale output is produced when the converter is configured with a 4.096V reference, and the analog-input differential is 4.096V. The negative full-scale output is produced when the differential voltage is -4.096V. In each case, the actual input voltages must remain within the -0.3V to  $+V_{\rm DD}$  range.

**Actual Analog-Input Voltage**—the voltage at any one analog input relative to GND.

**Full-Scale Range (FSR)**—as with most A/D converters, the full-scale range of the ADS1251 is defined as the input which produces the positive full-scale digital output minus the input which produces the negative full-scale digital output. For example, when the converter is configured with a 4.096V reference, the differential full-scale range is:

[4.096V (positive full-scale) - (-4.096V) (negative full-scale)] = 8.192V

Least Significant Bit (LSB) Weight—this is the theoretical amount of voltage that the differential voltage at the analog input would have to change in order to observe a change in the output data of one least significant bit. It is computed as follows:

$$LSB Weight = \frac{Full-ScaleRange}{2^{N}-1} = \frac{2 \cdot V_{REF}}{2^{N}-1}$$

where N is the number of bits in the digital output.

**Conversion Cycle**—as used here, a conversion cycle refers to the time period between DOUT/DRDY pulses.

**Effective Resolution (ER)**—of the ADS1251, in a particular configuration, can be expressed in two different units: bits rms (referenced to output) and  $\mu Vrms$  (referenced to input). Computed directly from the converter's output data, each is a statistical calculation based on a given number of results. Noise occurs randomly; the rms value represents a statistical measure, which is one standard deviation. The ER in bits can be computed as follows:

ER in bits rms =

$$\frac{20 \bullet log \left( \frac{2 \bullet V_{REF}}{Vrms \, noise} \right)}{6.02}$$

The  $2 \cdot V_{REF}$  figure in each calculation represents the full-scale range of the ADS1251. This means that both units are absolute expressions of resolution—the performance in different configurations can be directly compared, regardless of the units.

$f_{\text{MOD}}$ —frequency of the modulator and the frequency the input is sampled.

$$f_{MOD} = \frac{CLK \, Frequency}{6}$$

**f**<sub>DATA</sub>—Data output rate.

$$f_{DATA} = \frac{f_{MOD}}{64} = \frac{CLK Frequency}{384}$$

**Noise Reduction**—for random noise, the ER can be improved with averaging. The result is the reduction in noise by the factor  $\sqrt{N}$ , where N is the number of averages, as shown in Table IV. This can be used to achieve true 24-bit performance at a lower data rate. To achieve 24 bits of resolution, more than 24 bits must be accumulated. A 36-bit accumulator is required to achieve an ER of 24 bits. The following uses  $V_{REF} = 4.096V$ , with the ADS1251 outputting data at 20kHz, a 4096 point average will take 204.8ms. The benefits of averaging will be degraded if the input signal drifts during that 200ms.

| N<br>(Number<br>of Averages) | NOISE<br>REDUCTION<br>FACTOR | ER<br>IN<br>μVrms | ER<br>IN<br>BITS rms |

|------------------------------|------------------------------|-------------------|----------------------|

| 1                            | 1                            | 16μV              | 19.26                |

| 2                            | 1.414                        | 11.3μV            | 19.75                |

| 4                            | 2                            | 8μV               | 20.26                |

| 8                            | 2.82                         | 2.82 5.66μV       |                      |

| 16                           | 4                            | 4µV               | 21.26                |

| 32                           | 5.66 2.83μV                  |                   | 21.76                |

| 64                           | 64 8 2μV                     |                   | 22.26                |

| 128                          | 11.3                         | 1.41μV            | 22.76                |

| 256                          | 16                           | 1μV               | 23.26                |

| 512                          | 22.6                         | 0.71μV            | 23.76                |

| 1024                         | 1024 32                      |                   | 24.26                |

| 2048                         | 2048 45.25 0.35μV            |                   | 24.76                |

| 4096                         | 64                           | 0.25μV            | 25.26                |

TABLE IV. Averaging for Noise Reduction.

## **Revision History**

| DATE | REVISION | PAGE | SECTION   | DESCRIPTION                                      |

|------|----------|------|-----------|--------------------------------------------------|

| 9/07 | С        | 12   | Table II  | Changed t <sub>11</sub> from 1 • CLK to 3 • CLK. |

| 6/06 | В        | 11   | DOUT/DRDY | Text changes to DOUT/DRDY section.               |

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

.com 6-Sep-2007

#### PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| ADS1251U         | ACTIVE                | SOIC            | D                  | 8    | 100            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| ADS1251U/2K5     | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| ADS1251U/2K5G4   | ACTIVE                | SOIC            | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| ADS1251UG4       | ACTIVE                | SOIC            | D                  | 8    | 100            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

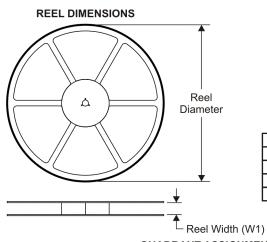

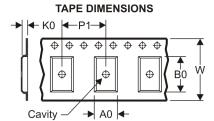

#### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       |      | Package<br>Drawing |   |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------|--------------------|---|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| ADS1251U/2K5 | SOIC | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4     | 5.2     | 2.1     | 8.0        | 12.0      | Q1               |

#### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| ADS1251U/2K5 | SOIC         | D               | 8    | 2500 | 346.0       | 346.0      | 29.0        |

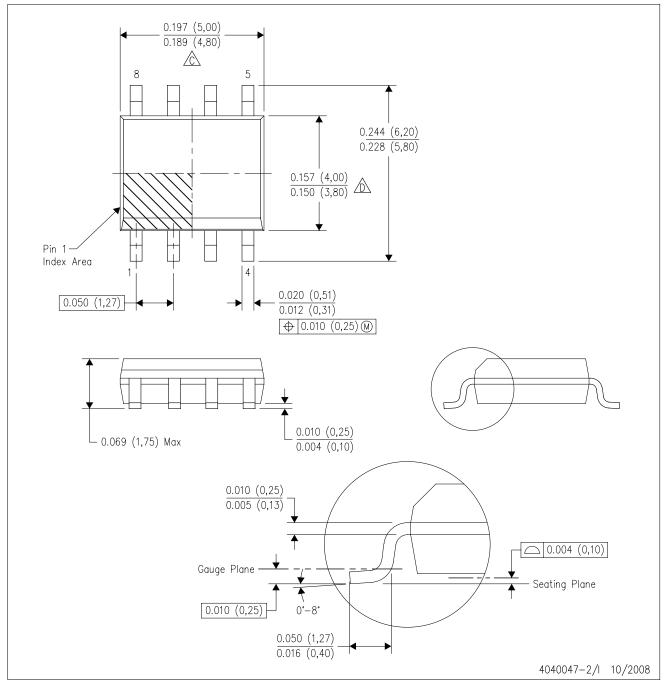

## D (R-PDSO-G8)

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 (0,15) per end.

- Body width does not include interlead flash. Interlead flash shall not exceed .017 (0,43) per side.

- E. Reference JEDEC MS-012 variation AA.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### **Products Amplifiers** amplifier.ti.com Data Converters dataconverter.ti.com DSP dsp.ti.com Clocks and Timers www.ti.com/clocks Interface interface.ti.com Logic logic.ti.com Power Mgmt power.ti.com Microcontrollers microcontroller.ti.com www.ti-rfid.com RF/IF and ZigBee® Solutions www.ti.com/lprf

| Applications       |                           |

|--------------------|---------------------------|

| Audio              | www.ti.com/audio          |

| Automotive         | www.ti.com/automotive     |

| Broadband          | www.ti.com/broadband      |

| Digital Control    | www.ti.com/digitalcontrol |

| Medical            | www.ti.com/medical        |

| Military           | www.ti.com/military       |

| Optical Networking | www.ti.com/opticalnetwork |

| Security           | www.ti.com/security       |

| Telephony          | www.ti.com/telephony      |

| Video & Imaging    | www.ti.com/video          |

| Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated